**Programming Specification**

### Introduction

This document provides instructions to help programming vendors qualify the SST FlashFlex microcontrollers.

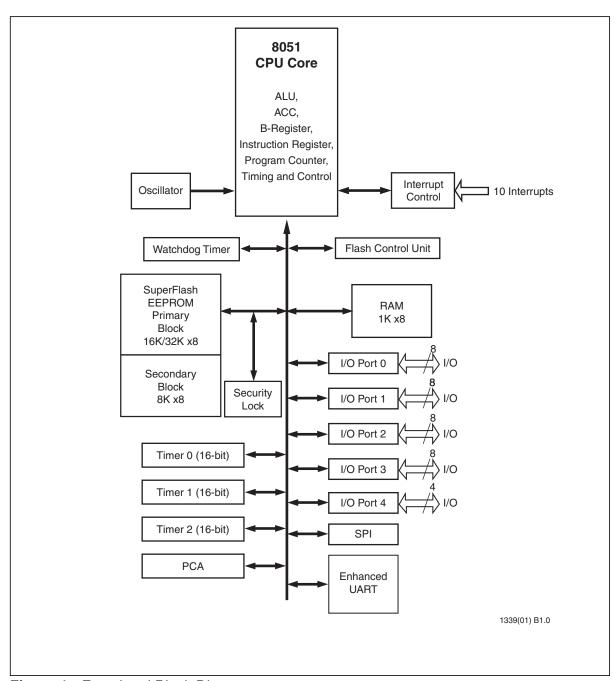

### **Functional Blocks**

Figure 1: Functional Block Diagram

**Programming Specification**

### **Flash Memory Programming**

The device's internal flash memory can be programmed or erased using the External Host Programming mode.

### **External Host Programming Mode**

External host programming mode allows the user to program the flash memory directly without using the CPU, see Table 1. External host mode is entered by forcing PSEN# from a logic high to a logic low while RST input is held continuously high. The device will stay in external host mode as long as RST = 1 and PSEN# = 0.

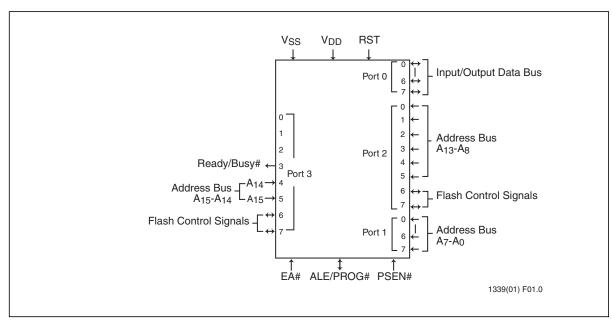

A Read-ID operation is necessary to "arm" the device in external host mode, and no other external host mode commands can be enabled until a Read-ID is performed. In external host mode, the internal flash memory blocks are accessed through the re-assigned I/O port pins by an external host, such as a MCU programmer, a PCB tester, or a PC-controlled development board. See Figure 2 for I/O port pin details.

**Table 1:** External Host Mode Commands<sup>1</sup>

| Operation           | RST              | PSEN#           | PROG#/<br>ALE   | EA#             | P3[7]           | P3[6]           | P2[7]           | P2[6]           | P0[7:0] | P3[5:4]<br>P2[5:0] | P1[7:0] |

|---------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------|--------------------|---------|

| Read-ID             | V <sub>IH1</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | DO      | AH                 | AL      |

| Chip-Erase          | V <sub>IH1</sub> | V <sub>IL</sub> | <b>↓</b> 12     | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Х       | Х                  | Х       |

| Block-Erase         | V <sub>IH1</sub> | V <sub>IL</sub> | $\downarrow$    | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Х       | Х                  | Х       |

| Sector-Erase        | V <sub>IH1</sub> | V <sub>IL</sub> | ↓               | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Х       | AH                 | AL      |

| Byte-Program        | V <sub>IH1</sub> | V <sub>IL</sub> | $\downarrow$    | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | DI      | AH                 | AL      |

| Byte-Verify (Read)  | V <sub>IH1</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | DO      | AH                 | AL      |

| Select-Block0       | V <sub>IH1</sub> | V <sub>IL</sub> | ↓               | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Х       | 55H                | Х       |

| Select-Block1       | V <sub>IH1</sub> | V <sub>IL</sub> | $\downarrow$    | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Х       | A5H                | Х       |

| Prog-SC0            | V <sub>IH1</sub> | V <sub>IL</sub> | $\downarrow$    | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Х       | 5AH                | Х       |

| Prog-SC1            | V <sub>IH1</sub> | V <sub>IL</sub> | ↓               | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Х       | AAH                | Х       |

| Prog-SB1            | V <sub>IH1</sub> | V <sub>IL</sub> | $\downarrow$    | V <sub>IH</sub> | Х       | Х                  | Х       |

| Prog-SB2            | V <sub>IH1</sub> | V <sub>IL</sub> | $\downarrow$    | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Х       | Х                  | Х       |

| Prog-SB3            | V <sub>IH1</sub> | V <sub>IL</sub> | $\downarrow$    | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Х       | Х                  | Х       |

| Enable-Clock-Double | V <sub>IH1</sub> | V <sub>IL</sub> | $\downarrow$    | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | Х       | 55H                | Х       |

T0-0.0 25115

Note: V<sub>IL</sub> = Input Low Voltage; V<sub>IH</sub> = Input High Voltage; V<sub>IH</sub> = Input High Voltage (XTAL, RST); X = Don't care; AL = Address low order byte; AH = Address high order byte; DI = Data Input; DO = Data Output.

<sup>1.</sup> External Host programming mode is guaranteed at 25°C (room temperature) only

<sup>2.</sup> Symbol <sup>↓</sup> signifies a negative pulse and the command is asserted during the low state of PROG#/ALE input. All other combinations of the above input pins are invalid and may result in unexpected behaviors.

**Programming Specification**

Figure 2: I/O Pin Assignments for External Host Mode

#### **Product Identification**

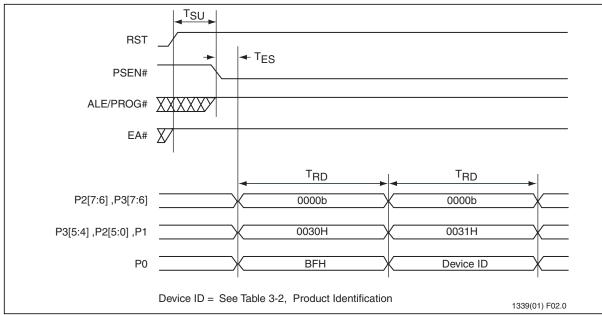

The Read-ID command accesses the signature bytes that reads and returns the device ID and identifies the manufacturer as SST, see Table 2. External programmers primarily use these signature bytes in the selection of programming algorithms. The Read-ID command is selected by the command code of 0H on P3[7:6] and P2[7:6]. See Figure 3 for timing waveforms.

Table 2: Product Identification

|                   | Address | Data |

|-------------------|---------|------|

| Manufacturer's ID | 30H     | BFH  |

| Device ID         |         |      |

| SST89E54RD2A/RDA  | 31H     | 9FH  |

| SST89E58RD2A/RDA  | 31H     | 9BH  |

T0-0 0 25115

### **Arming Command**

An arming command sequence must take place before any external host mode sequence command is recognized by the device. This prevents accidental triggering of external host mode commands due to noise or programmer error. The arming command is as follows:

- 1. PSEN# goes low while RST is high. This sets the machine in external host mode, re-configuring the pins, and turning on the on-chip oscillator.

- A Read-ID command is issued, and after 1 ms the external host mode commands can be issued.

After the above sequence, all other external host mode commands are enabled. Before the Read-ID command is received, all other external host mode commands received are ignored.

**Programming Specification**

#### **External Host Mode Commands**

The external host mode commands are Read-ID, Chip-Erase, Block-Erase, Sector-Erase, Byte-Program, Byte-Verify, Prog-SB1, Prog-SB2, Prog-SB3, Prog-SC0, Select-Block0, Select-Block1. See Table 1 for all signal logic assignments, Figure 2 for I/O pin assignments, and Table 4 for the timing parameters. The critical timing for all Erase and Program commands is generated by an on-chip flash memory controller. The high-to-low transition of the PROG# signal initiates the Erase or Program commands, which are synchronized internally. The Read commands are asynchronous reads, independent of the PROG# signal level. A detailed description of the external host mode commands follows.

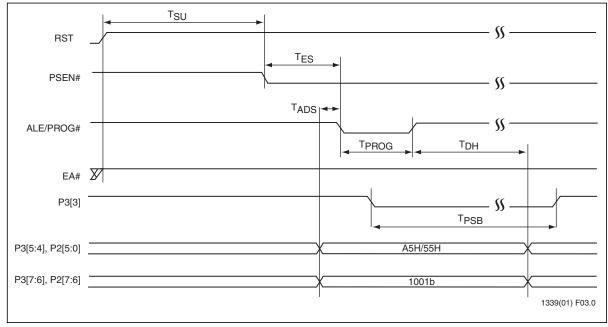

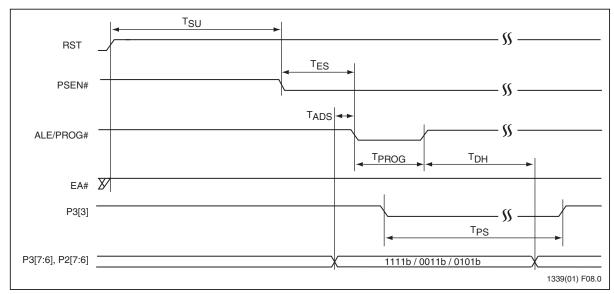

The Select-Block0 command enables Block 0 to be programmed in external host mode. Once this command is executed, all subsequent external host Commands will be directed at Block 0. See Figure 4 for timing waveforms.

The Select-Block1 command enables Block 1 (8 KByte Block) to be programmed. Once this command is executed, all subsequent external host Commands that are directed to the address range below 2000H will be directed at Block 1. The Select-Block1 command only affects the lowest 8 KByte of the program address space. For addresses greater than or equal to 2000H, Block 0 is accessed by default. Upon entering external host mode, Block 1 is selected by default. See Figure 4 for timing waveforms.

The Chip-Erase, Block-Erase, and Sector-Erase commands are used for erasing all or part of the memory array. Erased data bytes in the memory array will be erased to FFH. Memory locations that are to be programmed must be in the erased state prior to programming.

The Chip-Erase command erases all bytes in both memory blocks, regardless of any previous Select-Block0 or Select-Block1 commands. Chip-Erase ignores the Security Lock status and will erase the Security Lock, returning the device to its Unlocked state. The Chip-Erase command will also erase the SC0 bit. Upon completion of Chip-Erase command, Block 1 will be the selected block. See Figure 5 for timing waveforms.

The Block-Erase command erases all bytes in the selected memory blocks. This command will not be executed if the security lock is enabled. The selection of the memory block to be erased is determined by the prior execution Select-Block0 or Select-Block1 command. See Figure 6 for the timing waveforms.

The Sector-Erase command erases all of the bytes in a sector. The sector size for the flash memory is 128 Bytes. This command will not be executed if the Security lock is enabled. See Figure 7 for timing waveforms.

The Byte-Program command is used for programming new data into the memory array. Programming will not take place if any security locks are enabled. See Figure 8 for timing waveforms.

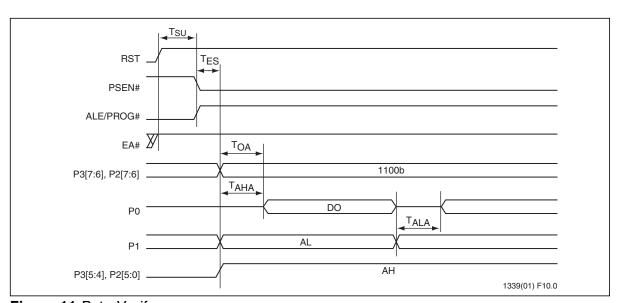

The Byte-Verify command allows the user to verify that the device correctly performed an Erase or Program command. This command will be disabled if any security locks are enabled. See Figure 11 for timing waveforms.

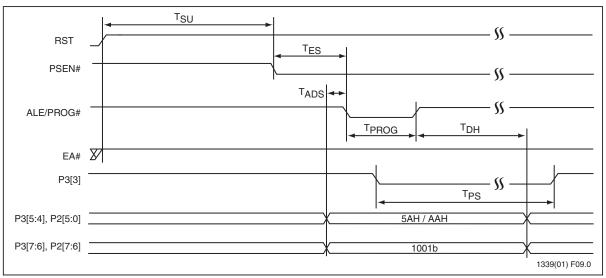

The Prog-SB1, Prog-SB2, Prog-SB3 commands program the security bits, the functions of these bits are described in the Security Lock section and also in Table 9-1. Once programmed, these bits can only be erased through a Chip-Erase command. See Figure 9 for timing waveforms.

Prog-SC0 command programs SC0 bit, which determines the state of SFCF[0] out of reset. Once programmed, SC0 can only be restored to an erased state via a Chip-Erase command. See Figure 10 for timing waveforms.

Programming Specification

#### **External Host Mode Clock Source**

In external host mode, an internal oscillator will provide clocking for the device, and the oscillator is unaffected by the clock doubler logic. The on-chip oscillator will be turned on as the device enters external host mode; i.e. when PSEN# goes low while RST is high. During external host mode, the CPU core is held in reset. Upon exit from external host mode, the internal oscillator is turned off.

#### Flash Operation Status Detection Via External Host Handshake

The device provides two methods for an external host to detect the completion of a flash memory operation to optimize the Program or Erase time. The end of a flash memory operation cycle can be detected by:

- 1. monitoring the Ready/Busy# bit at P3[3];

- 2. monitoring the Data# Polling bit at P0[3].

#### Ready/Busy# (P3[3])

The progress of the flash memory programming can be monitored by the Ready/Busy# output signal. P3[3] is driven low, some time after ALE/PROG# goes low during a flash memory operation to indicate the Busy# status of the Flash Control Unit (FCU). P3[3] is driven high when the flash programming operation is completed to indicate the ready status.

#### Data# Polling (P0[3])

During a Program operation, any attempts to read (Byte-Verify), while the device is busy, will receive the complement of the data of the last byte loaded (logic low, i.e. "0" for an Erase) on P0[3] with the rest of the bits "0". During a Program operation, the Byte-Verify command is reading the data of the last byte loaded, not the data at the address specified.

#### Instructions to Perform External Host Mode Commands

To program data into the memory array, apply power supply voltage  $(V_{DD})$  to  $V_{DD}$  and RST pins, and perform the following steps:

- 1. Maintain RST high and set PSEN# from logic high to low, in sequence according to the appropriate timing diagram.

- 2. Raise EA# High (VIH).

- 3. Issue Read-ID command to enable the external host mode.

- 4. Verify that the memory blocks or sectors for programming is in the erased state, FFH. If they are not erased, then erase them using the appropriate Erase command.

- 5. Select the memory location using the address lines (P3[5:4], P2[5:0], P1[7:0]).

- 6. Present the data in on P0[7:0].

- 7. Pulse ALE/PROG#, observing minimum pulse width.

- 8. Wait for low to high transition on Ready/Busy# (P3[3]).

- 9. Repeat steps 5 8 until programming is finished.

- 10. Verify the flash memory contents.

**Programming Specification**

#### **Additional Read Commands in External Host Mode**

The procedure to issue additional read commands, shown in Table 3 below, is the same as the read ID command format, only the address is changed. Here is a short list of useful features:

- Read the status of the security bits (SB1\_i, SB2\_i, SB3\_i).

- Read the configuration bits (SC0\_i) status.

- Read the clock mode (EDC\_i) status.

Note: Commands shown in Table 3 are not the ARMING type.

Table 3: Additional Read Commands in External Host Mode

| Address | Data |   |   |   |       |       |       |       |

|---------|------|---|---|---|-------|-------|-------|-------|

| 60H     | Х    | Х | Х | Х | SC0_i | SB1_i | SB2_i | SB3_i |

| 61H     | Х    | Х | Х | Х | Х     | Х     | EDC_i | Х     |

Note: X = Don't care

**Programming Specification**

Table 4: External Mode Flash Memory Programming/Verification Parameters<sup>1</sup>

| Parameter <sup>2,3</sup>                | Symbol            | Min | Max | Units |

|-----------------------------------------|-------------------|-----|-----|-------|

| Reset Setup Time                        | T <sub>SU</sub>   | 3   |     | μs    |

| Read-ID Command Width                   | T <sub>RD</sub>   | 1   |     | μs    |

| PSEN# Setup Time                        | T <sub>ES</sub>   | 40  |     | μs    |

| Address, Command, Data Setup<br>Time    | T <sub>ADS</sub>  | 0   |     | ns    |

| Chip-Erase Time                         | T <sub>CE</sub>   |     | 150 | ms    |

| Block-Erase Time                        | T <sub>BE</sub>   |     | 100 | ms    |

| Sector-Erase Time                       | T <sub>SE</sub>   |     | 30  | ms    |

| Program Setup Time                      | T <sub>PROG</sub> | 1.2 |     | μs    |

| Address, Command, Data Hold             | T <sub>DH</sub>   | 0   |     | ns    |

| Byte-Program Time <sup>4</sup>          | T <sub>PB</sub>   |     | 50  | μs    |

| Select-Block Program Time               | T <sub>PSB</sub>  |     | 500 | ns    |

| Re-map or Security bit Program<br>Time  | T <sub>PS</sub>   |     | 80  | μs    |

| Verify Command Delay Time               | T <sub>OA</sub>   |     | 50  | ns    |

| Verify High Order Address Delay<br>Time | T <sub>AHA</sub>  |     | 50  | ns    |

| Verify Low Order Address Delay<br>Time  | T <sub>ALA</sub>  |     | 50  | ns    |

T0-0.0 25115

- 1. For IAP operations, the program execution overhead must be added to the above timing parameters.

- 2. Program and Erase times will scale inversely proportional to programming clock frequency.

- 3. All timing measurements are from the 50% of the input to 50% of the output.

- 4. Each byte must be erased before programming.

**Programming Specification**

### Flash Memory Programming Timing Diagrams with External Host Mode

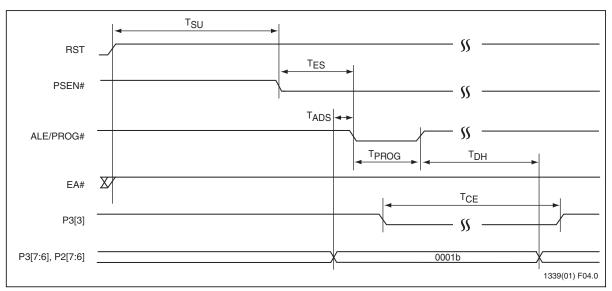

Figure 3: Read-ID

Reads chip signature and identification registers at the addressed location.

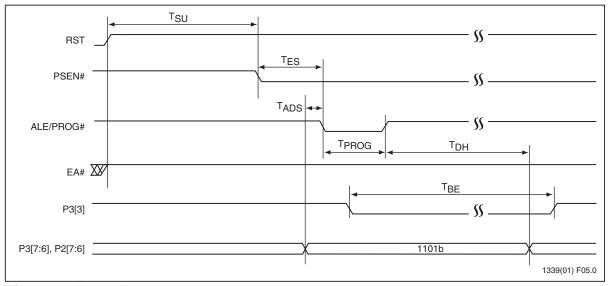

Figure 4: Select-Block1 / Select-Block0

Enables the selection of either of the flash memory blocks prior to issuing a Byte-Verify, Block-Erase, Sector-Erase, or Byte-Program.

**Programming Specification**

Figure 5: Chip-Erase

Erases both flash memory blocks. Security lock is ignored and the security bits are erased too.

Figure 6: Block-Erase

Erases one of the flash memory blocks, if the security lock is not activated on that flash memory block.

**Programming Specification**

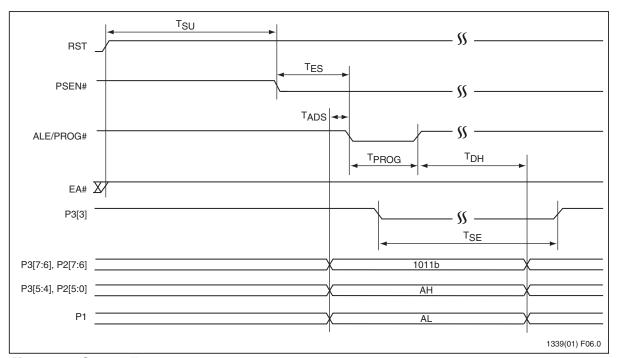

Figure 7: Sector-Erase

Erases the addressed sector if the security lock is not activated on that flash memory block.

**Programming Specification**

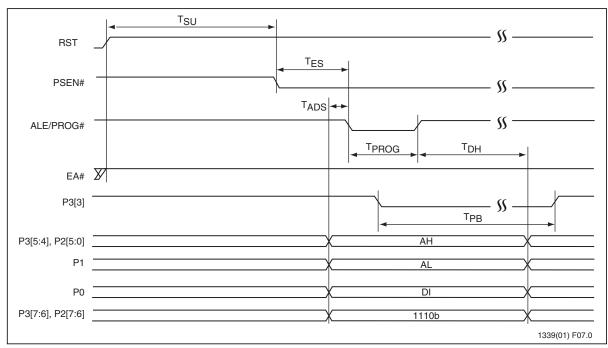

Figure 8: Byte-Program

Programs the addressed code byte if the byte location has been successfully erased and not yet programmed. Byte-Program operation is only allowed when the security lock is not activated on that flash memory block.

Figure 9: Prog-SB1 / Prog-SB2 / Prog-SB3

Programs the Security bits SB1, SB2 and SB3 respectively. Only a Chip-Erase will erase a programmed security bit.

**Programming Specification**

Figure 10: Prog-SC0

Programs the start-up configuration bit SC0. Only a Chip-Erase will erase a programmed SC0 bit.

Figure 11: Byte-Verify

Reads the code byte from the addressed flash memory location if the security lock is not activated on that flash memory block.

**Programming Specification**

#### Table 5: Revision History

| Revision | Description |                                                      |          |  |  |

|----------|-------------|------------------------------------------------------|----------|--|--|

| 00       | •           | Initial release of programming spec                  | Nov 2006 |  |  |

| 01       | •           | Removed SST89V54RD2A/RDA / SST89V58RD2A/RDA globally | Feb 2008 |  |  |

| Α        | •           | Applied new document format                          | Dec 2011 |  |  |

|          | •           | Released document under letter revision system       |          |  |  |

|          | •           | Updated Spec number from S71339(01) to DS25115       |          |  |  |

#### ISBN:978-1-61341-896-3

© 2011 Silicon Storage Technology, Inc-a Microchip Technology Company. All rights reserved.

SST, Silicon Storage Technology, the SST logo, SuperFlash, MTP, and FlashFlex are registered trademarks of Silicon Storage Technology, Inc. MPF, SQI, Serial Quad I/O, and Z-Scale are trademarks of Silicon Storage Technology, Inc. All other trademarks and registered trademarks mentioned herein are the property of their respective owners.

Specifications are subject to change without notice. Refer to www.microchip.com for the most recent documentation. For the most current package drawings, please see the Packaging Specification located at http://www.microchip.com/packaging.

Memory sizes denote raw storage capacity; actual usable capacity may be less.

SST makes no warranty for the use of its products other than those expressly contained in the Standard Terms and Conditions of Sale.

For sales office locations and information, please see www.microchip.com.

Silicon Storage Technology, Inc. A Microchip Technology Company www.microchip.com